# Index- Computer Organization and Architecture

| <u>Sl.No.</u> | <u>Name of the Topic</u> |

|---------------|--------------------------|

| 1.            | Co Introduction          |

| 2.            | Memory Interface         |

| 3.            | Storage Manager          |

| 4.            | Addressing Modes         |

| 5.            | DMA                      |

| 6.            | Instruction Pipelining   |

| 7.            | Data & Control Modes     |

#### Common Data for Q1 Q2 and Q3 is given below

Consider a machine a 2-way set associative data cache of size 64 kbytes and block size 16 bytes. The cache is managed using 32 bit virtual addressed and the page size is 4 Kbytes. A program to be run on this machine begins as follows. double APR[1024] [1024] int i,j; /\*initalize array APR to 0.0\*/ for [i=0; i <1024; i++) for (j=0; k <1024;j++ ARR [i][j]=0.0; The size of double 8 bytes. Array APR is in memory starting at the beginning of virtual page 0 x FF000 and stored in row major order. The cache is initially empty and no pre-fetching is done. The only data memory references made by the program are those to array APR... <sup>1)</sup>The total size of the tags in the cache directory is 2 Marks GATE-CSE/IT-2008,GATE-CSE/IT-2008,GATE-CSE/IT-2008,GATE-CSE/IT-2008() [A] 32kbits [B]34kbits [C]64kbits [D]68kbits <sup>2)</sup>Which of the following array elements has the same cache index as APR[0] [0]? 2 Marks GATE-CSE/IT-2008( ) [A]APR[0][4] [B]APR[4] [0] [C]ARR[0][5] [D]APR[5][0] <sup>3)</sup>The cache hit ratio for this initialization loop is 2 Marks GATE-CSE/IT-2008,GATE-CSE/IT-2008( ) [A]0% [B] 25% [C]50% [D]75% Common Data for Q4 and Q5 is given below Consider a machine with a byte addressable main memory of 2<sup>16</sup> bytes. Assume that a direct mapped data cache consisting of 32 lines of 64 bytes each is used in the system. A 50 x 50 two-dimensional array of bytes is stored in the main memory starting from memory location 1100

H. Assume that the data cache is initially empty. The complete array is accessed twice. Assume that the contents of the data cache do not change in between the two accesses.

2 Marks GATE-CSE/IT-2007()

<sup>4)</sup> How many data cache misses will occur in total?

| [A]40 | [B]50 |

|-------|-------|

| [C]56 | [D]59 |

<sup>5)</sup> Which of the following lines of the data cache will be replaced by new blocks in accessing the array <sup>2</sup> Marks GATE-CSE/IT-2007, GAT

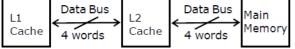

|                        | Common Data for Q7 and Q6 is given below |

|------------------------|------------------------------------------|

| [C]line 0 to line 7    | [D]line 0 to line 8                      |

| [A] line 4 to line 1 1 | [B] line 4 to line 12                    |

A CPU has a 32 KB direct mapped cache with 128-byte block size. Suppose A is a two dimensional array of size  $512 \times 512$  with elements that occupy 8-bytes each/ Consider the following two C code segments, P1 and P2. P1: for (i=0; i < 512; i++){ for (j=0; j < 512; j++){ x + = A[i][i];} } P2: for (i=0; i < 512; i++){ for (j=0; j < 512; j++) {  ${x + = A[j] [i];}$ } P1 and P2 are executed independently with the same initial state, namely, the array A is not in the cache and i,j, x are in registers. Let the number of cache misses experienced by P1 be  $M_1$  and that for P2 be  $M_2$ . <sup>6)</sup>The value of M<sub>1</sub> is 2 Marks GATE-CSE/IT-2006( ) [A]0 [B]2048 [C]16384 [D]262144 <sup>7)</sup> The value of the ratio  $M_1 / M_2$  is 2 Marks GATE-CSE/IT-2006,GATE-CSE/IT-2006( ) [A]0 [B]1/16 [C]1/8 [D]16 Common Data for Q8 and Q9 is given below Consider two cache organizations : The first one is 32 KB2-way set associative with 32-byte block size. The second one is of the same size but direct mapped. The size of an address is 32 bits in both cases A 2-to 1 multiplexer has latency of 0.6ns while a k-bit comparator has a latency of k/10-ns. The hit latency of the set associative organization is  $h_1$  while that of the direct mapped one is  $h_2$ . <sup>8)</sup>The value of h1 is 2 Marks GATE-CSE/IT-2006,GATE-CSE/IT-2006( ) [A]2.4ns [B] 2.3ns [C]1.8ns [D]1.7ns <sup>9)</sup>The value of h<sub>2</sub> is 2 Marks GATE-CSE/IT-2006( ) [A]2.4ns [B] 2.3ns [C]1.8ns [D]1.7ns Common Data for Q10 and Q11 is given below Consider two cache organizations : The first one is 32 KB 2-way set associative with 32-byte block size. The second one is of the same size but direct mapped. The size of an address is 32 bits in both cases A 2-to 1 multiplexer has latency of 0.6ns while a k-bit comparator has a latency of k/1-ns. The hit latency of the set associative organization is h1 while that of the direct mapped one is h2. <sup>10)</sup>The value of h1 is 2 Marks GATE-CSE/IT-2006( ) [A]2.4ns [B] 2.3ns [C]1.8ns [D]1.7ns <sup>11)</sup>The value of h2 is 2 Marks GATE-CSE/IT-2006( ) [A]2.4ns [B] 2.3ns [C]1.8ns [D]1.7ns <sup>12)</sup>Consider a small two-way set-associative cache memory, consitsting of four blocks. For choosing the block to be replace, use the least recently used (LRU) scheme. The number of cache misses for the following sequence of block addresses is 8, 12, 0, 12, 8

|                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                              | 2 Marks GATE-CSE/IT-2004( )                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| [A]2<br>[C]4                                                                                                                                                                                                                                                                                                                                                                      | [B] 3<br>[D] 5                                                                                                                                                                               |                                                                                                                       |

| <sup>13)</sup> Increasing the RAM of a computer typically imp                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                              |                                                                                                                       |

| [A] Virtual memory increases                                                                                                                                                                                                                                                                                                                                                      | [B]Larger RAMs are faster                                                                                                                                                                    | 1 Marks GATE-CSE/IT-2005( )                                                                                           |

| [C]Fewer page faults occur                                                                                                                                                                                                                                                                                                                                                        | [D]Fewer segmentation fau                                                                                                                                                                    | ltsoccur                                                                                                              |

| <sup>14)</sup> Consider a direct mapped cache of size 32 KB addresses. The number of bits needed for cache                                                                                                                                                                                                                                                                        |                                                                                                                                                                                              |                                                                                                                       |

| [A]10,17<br>[C]15,17                                                                                                                                                                                                                                                                                                                                                              | [B]10,22<br>[D]5,17                                                                                                                                                                          | ()                                                                                                                    |

| <sup>15)</sup> A CPU has a cache with block size 64 bytes. The wide. Consecutive c-byte chunks are mapped of can be accessed in parallel, but two accesses to ay involve multiple iterations of parallel bank a accessing all the k banks in parallel. Each iterat in parallel and this takes k/2 ns. The latency of or retrieving a cache block starting at address zero.        | on consecutive banks with warp-are<br>o the same bank must be serialized.<br>ccesses depending on the amount o<br>ion requires decoding the bank nur<br>one bank access is 80 ns. If c=2 and | ound. All the k banks<br>A cache block access<br>of data obtained by<br>nbers to be accessed                          |

| [A] 92ns                                                                                                                                                                                                                                                                                                                                                                          | [B] 104ns                                                                                                                                                                                    | 2 Marks GATE-CSE/IT-2006( )                                                                                           |

| [C]172ns                                                                                                                                                                                                                                                                                                                                                                          | [D]184ns                                                                                                                                                                                     |                                                                                                                       |

| <sup>16)</sup> Consider a small two-way set-associative cache<br>block to be replace, use the least recently used<br>following sequence of block addresses is 8, 1                                                                                                                                                                                                                | (LRU) scheme. The number of cach                                                                                                                                                             | For choosing the<br>e misses for the                                                                                  |

| [A]2                                                                                                                                                                                                                                                                                                                                                                              | [B] 3                                                                                                                                                                                        | 2 Marks GATE-CSE/IT-2004()                                                                                            |

| [C]4                                                                                                                                                                                                                                                                                                                                                                              | [D]5                                                                                                                                                                                         |                                                                                                                       |

| <sup>17)</sup> Increasing the RAM of a computer typically imp                                                                                                                                                                                                                                                                                                                     | proves performance because                                                                                                                                                                   | 1 Marks GATE-CSE/IT-2005( )                                                                                           |

| [A] Virtual memory increases                                                                                                                                                                                                                                                                                                                                                      | [B]Larger RAMs are faster                                                                                                                                                                    |                                                                                                                       |

| [C]Fewer page faults occur                                                                                                                                                                                                                                                                                                                                                        | [D]Fewer segmentation fau                                                                                                                                                                    |                                                                                                                       |

| <sup>18)</sup> Consider a direct mapped cache of size 32 KB addresses. The number of bits needed for cache                                                                                                                                                                                                                                                                        |                                                                                                                                                                                              |                                                                                                                       |

| [A]10,17<br>[C]15,17                                                                                                                                                                                                                                                                                                                                                              | [B] 10,22<br>[D]5,17                                                                                                                                                                         |                                                                                                                       |

| <sup>19)</sup> A CPU has a cache with block size 64 bytes. Th<br>wide. Consecutive c-byte chunks are mapped<br>can be accessed in parallel, but two accesses to<br>ay involve multiple interations of parallel bank<br>accessing all the k banks in parallel. Each iterat<br>in parallel and this takes k/2 ns. The latency of<br>retrieving a cache block starting at address ze | on consecutive banks with warp-are<br>o the same bank must be serialized.<br>accesses depending on the amount<br>ion requires decoding the bank nur<br>one bank access is 80 ns. If c=2 and  | ound. All the k banks<br>A cache block access<br>of data obtained by<br>nbers to be accessed<br>k=24, then latency of |

| [A] 92ns                                                                                                                                                                                                                                                                                                                                                                          | [B]104ns                                                                                                                                                                                     | 2 Marks GATE-CSE/IT-2006( )                                                                                           |

| [C]172 ns                                                                                                                                                                                                                                                                                                                                                                         | [D]184 ns                                                                                                                                                                                    |                                                                                                                       |

| <sup>20)</sup> Consider 4-way set associative cache consisting<br>generates a 20-bit address of a word in main m<br>fields are respectively                                                                                                                                                                                                                                       |                                                                                                                                                                                              |                                                                                                                       |

| [A]9,6,5                                                                                                                                                                                                                                                                                                                                                                          | [B] 7,7,6                                                                                                                                                                                    | 1 Marks GATE-CSE/IT-2007()                                                                                            |

| [C]7,5,8                                                                                                                                                                                                                                                                                                                                                                          | [D]9,5,6                                                                                                                                                                                     |                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                              |                                                                                                                       |

| <ul> <li><sup>21)</sup> For inclusion to hold between two cache level L1 and following are necessary ?</li> <li>1. L1 must be a write-through cache</li> <li>2. L2 must be write-through cache</li> <li>3. The associativity of L2 must be greater that of</li> <li>4. The L2 cache must be at least as large as the L1</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | L1                                                                                   | y, which of the<br>2 Marks GATE-CSE/IT-2008() |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------|

| [A]4 only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | [B] and 2 only                                                                       | 2 Marks GATE-CSE/11-2006()                    |

| [C]1,2 and 4 only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | [D]1,2,3 and 4                                                                       |                                               |

| <sup>22)</sup> How many 32K x 1 RAM chips are needed to provid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | de a memory capacity of 256 K                                                        |                                               |

| [A] 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | [B] 32                                                                               | 1 Marks GATE-CSE/IT-2009( )                   |

| [C]64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | [D]128                                                                               |                                               |

| $^{23)}$ How many 32K x 1 RAM chips are needed to provid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | le a memory capacity of 256 K                                                        | -bytes ?                                      |

| [A] 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | [B] 32                                                                               | 1 Marks GATE-CSE/IT-2008()                    |

| [C]64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | [D]128                                                                               |                                               |

| <ul> <li><sup>24)</sup>Consider a 4 way set associative cache (initially empt consists of 256 blocks and the request for memor 0,255, 1,4,3,8,133, 159, 216, 129, 63, 8,48,32,7 Which one of the following memory block will NC</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | y) with total 16 cache blocks. Th<br>y blocks is in the following ord<br>73, 92, 155 | er :                                          |

| [A] 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | [B] 8                                                                                | 2 Marks GATE-CSE/11-2009()                    |

| [C]129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | [D]216                                                                               |                                               |

| <sup>25)</sup> The main memory of a computer has 2 cm blocks wh<br>associative mapping scheme with 2 blocks per set,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                      |                                               |

| [A] (k mod m) of the cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | [B] (k mod c) of the cache                                                           |                                               |

| [C](k mod 2c) of the cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | [D](k mod 2 cm) of the cache                                                         |                                               |

| <sup>26)</sup> Which of the following devices should get higher prio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rity in assigning interrupts?                                                        | 1 Marks GATE-CSE/IT-1998( )                   |

| [A] Hard disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | [B] Printer                                                                          | ·                                             |

| [C]keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | [D]Floppy disk                                                                       |                                               |

| <sup>27)</sup> Locality of reference implies that the page referenc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | e being made by a process                                                            | 1 Marks GATE-CSE/IT-1997( )                   |

| [A] will always be to the page used in the previous page reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | [B] is likely to be to one of the p<br>few page references                           |                                               |

| [C]will always be to one of the pages existing in<br>memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | [D]will always lead to a page                                                        | e fault                                       |

| <ul> <li><sup>28)</sup> A ROM is sued to store the table for multiplication of the store the</li></ul> | wo 8-bit unsigned integers.The                                                       | size of ROM required                          |

| [A]256 * 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | [B]64 k * 8                                                                          | 1 Marks GATE-CSE/IT-1996()                    |

| [C]4k * 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | [D]64k * 16                                                                          |                                               |

| <sup>29)</sup> Both's algorithm for integer multiplication gives we                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                      | ltiplier pattern is                           |